#### **TECHNOLOGY IN ACTION™**

# Beginning STM32

Developing with FreeRTOS, libopencm3 and GCC

Warren Gay

# **Beginning STM32**

Developing with FreeRTOS, libopencm3 and GCC

Warren Gay

Apress<sup>®</sup>

#### Beginning STM32: Developing with FreeRTOS, libopencm3 and GCC

Warren Gay St. Catharines, Ontario, Canada

#### ISBN-13 (pbk): 978-1-4842-3623-9 https://doi.org/10.1007/978-1-4842-3624-6

ISBN-13 (electronic): 978-1-4842-3624-6

Library of Congress Control Number: 2018945101

#### Copyright © 2018 by Warren Gay

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

Trademarked names, logos, and images may appear in this book. Rather than use a trademark symbol with every occurrence of a trademarked name, logo, or image we use the names, logos, and images only in an editorial fashion and to the benefit of the trademark owner, with no intention of infringement of the trademark.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Managing Director, Apress Media LLC: Welmoed Spahr Acquisitions Editor: Aaron Black Development Editor: James Markham Coordinating Editor: Jessica Vakili

Cover designed by eStudioCalamar

Cover image designed by Freepik (www.freepik.com)

Distributed to the book trade worldwide by Springer Science+Business Media New York, 233 Spring Street, 6th Floor, New York, NY 10013. Phone 1-800-SPRINGER, fax (201) 348-4505, email orders-ny@springer-sbm. com, or visit www.springeronline.com. Apress Media, LLC is a California LLC and the sole member (owner) is Springer Science + Business Media Finance Inc (SSBM Finance Inc). SSBM Finance Inc is a **Delaware** corporation.

For information on translations, please email rights@apress.com or visit http://www.apress.com/rights-permissions.

Apress titles may be purchased in bulk for academic, corporate, or promotional use. eBook versions and licenses are also available for most titles. For more information, reference our Print and eBook Bulk Sales web page at http://www.apress.com/bulk-sales.

Any source code or other supplementary material referenced by the author in this book is available to readers on GitHub via the book's product page, located at www.apress.com/978-1-4842-3623-9. For more detailed information, please visit http://www.apress.com/source-code.

Printed on acid-free paper

For Jackie

### **Table of Contents**

| About the Author             | xix |

|------------------------------|-----|

| About the Technical Reviewer | xxi |

| Chapter 1: Introduction      |     |

| STM32F103C8T6                | 2   |

| FreeRTOS                     | 5   |

| libopencm3                   | 5   |

| No Arduino                   | 6   |

| No IDE                       | 6   |

| Development Framework        | 7   |

| Assumptions About You        | 7   |

| What You Need                | 8   |

| ST-Link V2 Programming Unit  |     |

| Breadboard                   | 9   |

| DuPont (Jumper) Wires        |     |

| 0.1 uF Bypass Capacitors     |     |

| USB TTL Serial Adapter       |     |

| Power Supply                 |     |

| Small Stuff                  |     |

| Summary                      |     |

| Chapter 2: Software Setup    |     |

| Directory Conventions Used   |     |

| Operating Software           |     |

| Book Software                   |    |

|---------------------------------|----|

| libopencm3                      |    |

| FreeRTOS                        | 19 |

| ~/stm32f103c8t6/rtos/Project.mk | 19 |

| ARM Cross Compiler              |    |

| Build the Software              |    |

| ST-Link Tool                    |    |

| Summary                         |    |

| Chapter 3: Power Up and Blink   | 27 |

| Power                           |    |

| +3.3V Regulator                 |    |

| USB Power/+5V                   |    |

| +3.3V Supply                    | 30 |

| One Power Source Rule           |    |

| Ground                          |    |

| Reset                           |    |

| Showtime                        |    |

| ST-Link V2                      |    |

| st-flash Utility                |    |

| Read STM32                      |    |

| Write Image                     |    |

| Erase Flash                     |    |

| Summary                         |    |

| Bibliography                    |    |

| Chapter 4: GPIO                 | 39 |

| Building miniblink              |    |

| Flashing miniblink              | 40 |

| miniblink.c Source Code         | 41 |

| GPIO API                        |    |

| GPIO Configuration              |    |

| Ducks in a Row                    | 51 |

|-----------------------------------|----|

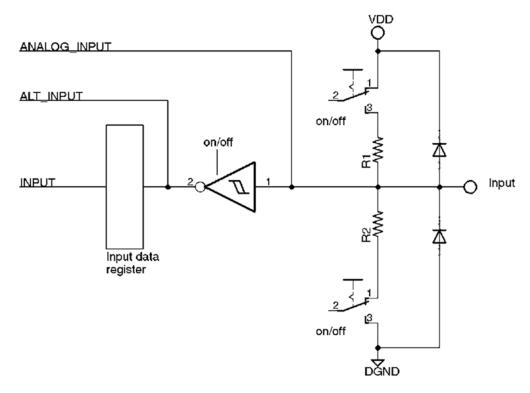

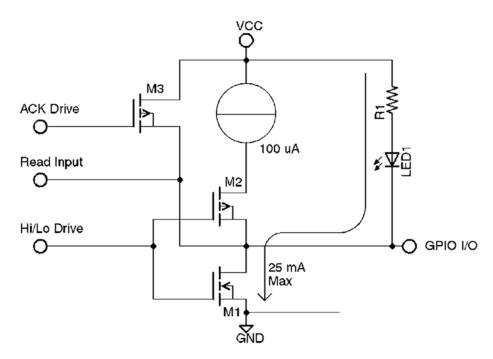

| GPIO Inputs                       | 51 |

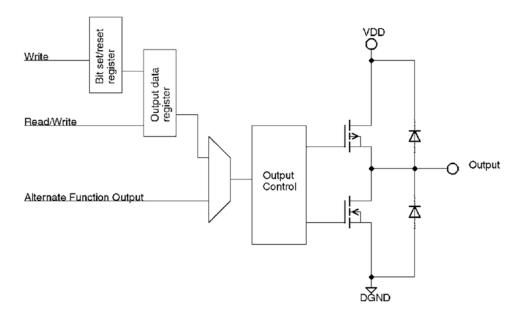

| Digital Output, Push/Pull         | 52 |

| Digital Output, Open Drain        | 53 |

| GPIO Characteristics              | 53 |

| Input Voltage Thresholds          | 55 |

| Output-Voltage Thresholds         | 55 |

| Programmed Delays                 | 56 |

| The Problem with Programmed Delay |    |

| Summary                           | 58 |

| Chapter 5: FreeRTOS               | 59 |

| FreeRTOS Facilities               |    |

| Tasking                           |    |

| Message Queues                    |    |

| Semaphores and Mutexes            |    |

| Timers                            |    |

| Event Groups                      |    |

| The blinky2 Program               |    |

| Build and Test blinky2            |    |

| Execution                         |    |

| FreeRTOSConfig.h                  | 67 |

| FreeRTOS Naming Convention        |    |

| FreeRTOS Macros                   |    |

| Summary                           |    |

|                                   |    |

| Chapter 6: USART                  |    |

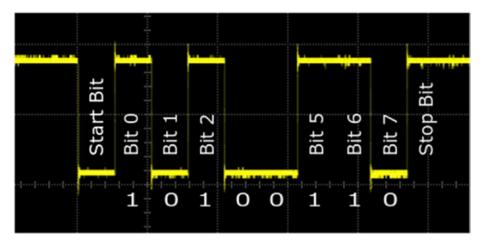

| USART/UART Peripheral             |    |

| Asynchronous Data                 |    |

| USB Serial Adapters               |    |

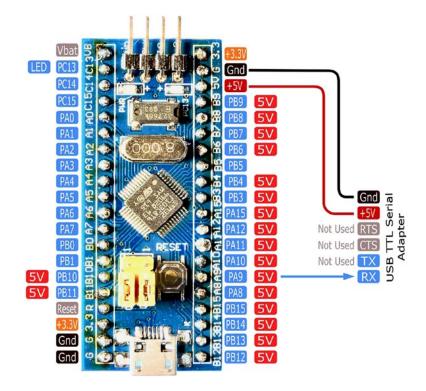

| Hookup                            |    |

| Project uart                      | 77 |

| Project                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Project uart2                                                                                                                                                                                                            |

| USART API                                                                                                                                                                                                                |

| Include Files                                                                                                                                                                                                            |

| Clocks                                                                                                                                                                                                                   |

| Configuration                                                                                                                                                                                                            |

| DMA                                                                                                                                                                                                                      |

| Interrupts9                                                                                                                                                                                                              |

| Input/Output/Status                                                                                                                                                                                                      |

| Ducks-in-a-Row                                                                                                                                                                                                           |

| FreeRTOS                                                                                                                                                                                                                 |

| Tasks                                                                                                                                                                                                                    |

| Queues                                                                                                                                                                                                                   |

| Summary                                                                                                                                                                                                                  |

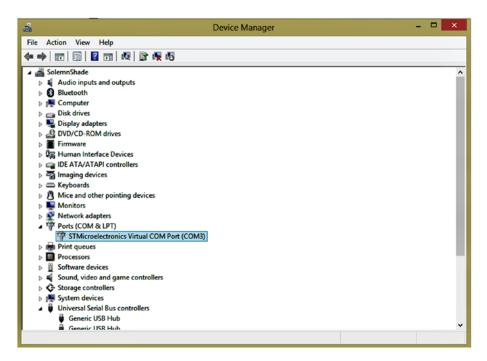

| Chapter 7: USB Serial                                                                                                                                                                                                    |

|                                                                                                                                                                                                                          |

| Blue Pill USB Issue                                                                                                                                                                                                      |

| Blue Pill USB Issue       9         Introduction to USB       9                                                                                                                                                          |

|                                                                                                                                                                                                                          |

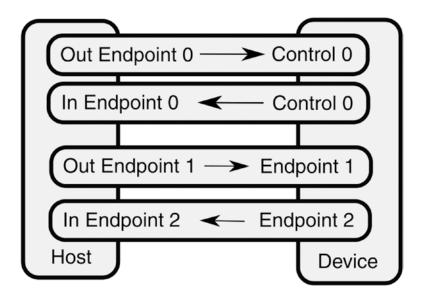

| Introduction to USB                                                                                                                                                                                                      |

| Introduction to USB9Pipes and Endpoints9USB Serial Device10Linux USB Serial Device10MacOS USB Serial Device10Windows USB Serial Device101010                                                                             |

| Introduction to USB9Pipes and Endpoints9USB Serial Device10Linux USB Serial Device10MacOS USB Serial Device10Windows USB Serial Device10USB GPI010                                                                       |

| Introduction to USB9Pipes and Endpoints9USB Serial Device10Linux USB Serial Device10MacOS USB Serial Device10Windows USB Serial Device10USB GPI010Demo Source Code10                                                     |

| Introduction to USB9Pipes and Endpoints9USB Serial Device10Linux USB Serial Device10MacOS USB Serial Device10Windows USB Serial Device10USB GPI010Demo Source Code10cdcacm_set_config()10                                |

| Introduction to USB99Pipes and Endpoints99USB Serial Device10Linux USB Serial Device10MacOS USB Serial Device10Windows USB Serial Device10USB GPI010Demo Source Code10cdcacm_set_config()10cdc_control_request()10       |

| Introduction to USB94Pipes and Endpoints94USB Serial Device107Linux USB Serial Device107MacOS USB Serial Device107Windows USB Serial Device107USB GPI0107Demo Source Code107cdcacm_set_config()107cdcacm_data_rx_cb()107 |

|   | USB Serial Demo                 | 111 |

|---|---------------------------------|-----|

|   | Summary                         | 113 |

|   | Bibliography                    | 114 |

| C | Chapter 8: SPI Flash            | 115 |

|   | Introducing W25QXX              | 115 |

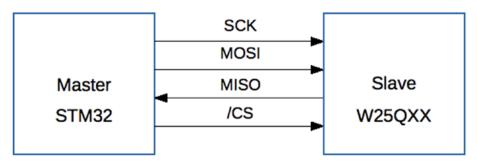

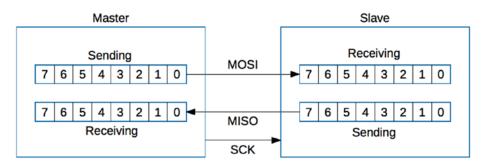

|   | Serial Peripheral Interface Bus | 115 |

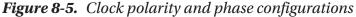

|   | Chip Select                     | 117 |

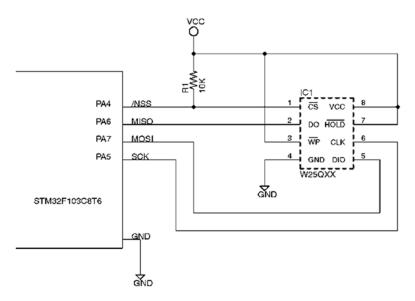

|   | Wiring and Voltages             | 117 |

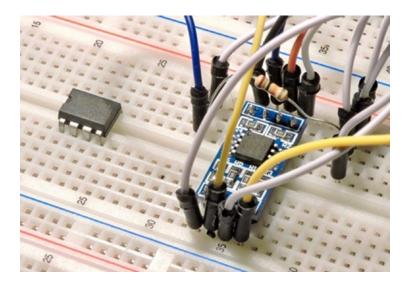

|   | SPI Circuit                     | 118 |

|   | Hardware /NSS Control           | 118 |

|   | STM32 SPI Configuration         | 120 |

|   | SPI Clock Rate                  | 124 |

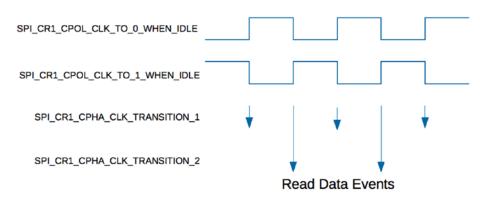

|   | SPI Clock Modes                 | 125 |

|   | Endianess and Word Length       | 127 |

|   | SPI I/O                         | 128 |

|   | Read SR1                        | 128 |

|   | Waiting for Ready               | 129 |

|   | Read Manufacturer ID            | 130 |

|   | Writing Flash                   | 131 |

|   | Flash Erase                     | 133 |

|   | Reading Flash                   | 136 |

|   | Demonstration                   | 137 |

|   | Running the Demo                | 139 |

|   | Manufacturer ID                 | 144 |

|   | Power Down                      | 144 |

|   | Summary                         | 145 |

|   | Bibliography                    | 145 |

|   |                                 |     |

| Chapter 9: Code Overlays          | 147 |

|-----------------------------------|-----|

| The Linker Challenge              | 147 |

| MEMORY Section                    | 149 |

| Entry                             | 151 |

| Sections                          | 151 |

| PROVIDE                           | 154 |

| Relocation                        | 154 |

| Defining Overlays                 | 155 |

| Overlay Code                      | 157 |

| Overlay Stubs                     | 159 |

| Overlay Manager                   | 159 |

| VMA and Load Addresses            | 160 |

| Linker Symbols in Code            | 161 |

| Overlay Manager Function          | 162 |

| Overlay Stubs                     | 164 |

| Demonstration                     | 165 |

| Extracting Overlays               | 166 |

| Upload Overlays to W25Q32         | 167 |

| Overlay Demo Continued            | 171 |

| Code Change Trap                  | 173 |

| Summary                           | 173 |

| Bibliography                      | 174 |

| Chapter 10: Real-Time Clock (RTC) |     |

| Demonstration Projects            |     |

| RTC Using One Interrupt           |     |

| RTC Configuration                 |     |

| Interrupt and Setup               |     |

| Interrupt Service Routine         |     |

| Task Notification                 |     |

| Mutexes                           |     |

| Demonstration               |     |

|-----------------------------|-----|

| UART1 Connections           |     |

| Running the Demo            |     |

| rtc_alarm_isr()             |     |

| EXTI Controller             |     |

| Summary                     | 192 |

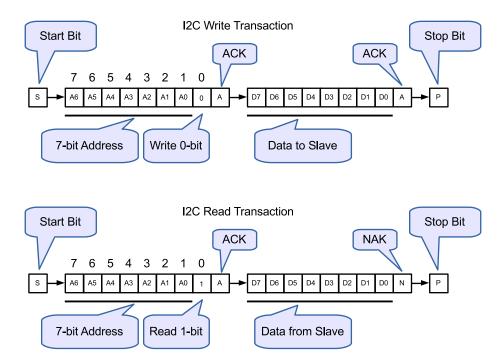

| Chapter 11: I2C             |     |

| The I2C Bus                 |     |

| Master and Slave            |     |

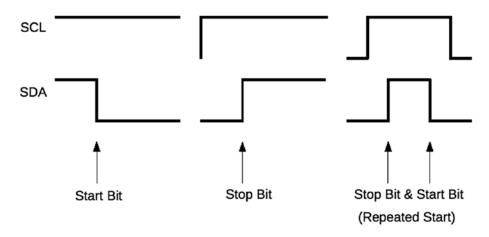

| Start and Stop              |     |

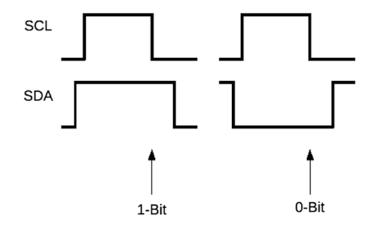

| Data Bits                   |     |

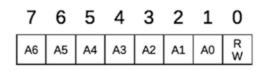

| I2C Address                 |     |

| I2C Transactions            |     |

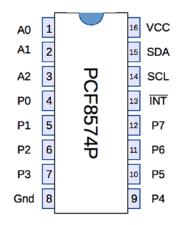

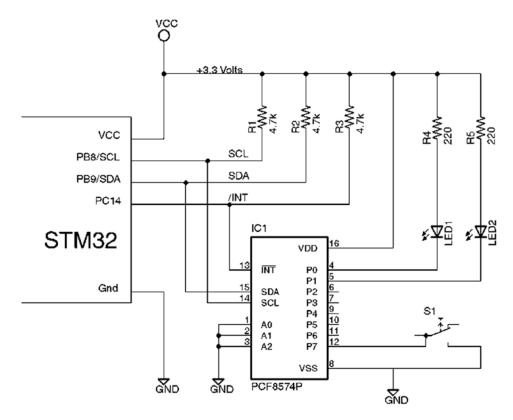

| PCF8574 GPIO Extender       |     |

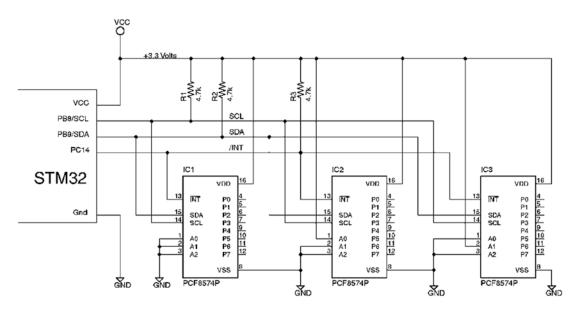

| I2C Circuit                 |     |

| The PCF8574 <i>INT</i> Line |     |

| PCF8574 Configuration       |     |

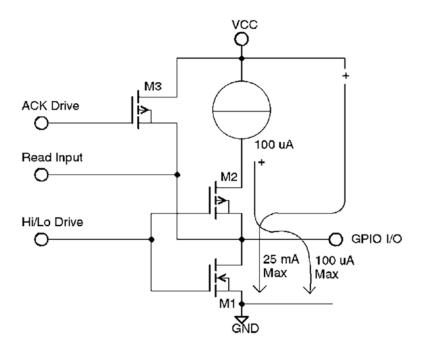

| PCF8574 GPIO Drive          |     |

| Wave Shaping                |     |

| Demo Circuit                |     |

| EXTI Interrupt              |     |

| I2C Software                |     |

| Testing I2C Ready           |     |

| Start I2C                   |     |

| I2C Write                   |     |

| I2C Read                    |     |

| I2C Restart                 |     |

| Demo Program                |     |

| Demo Session                |     |

| Summary                     |     |

|                             |     |

| Chapter 12: OLED                                                                                                                                                                                 |                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

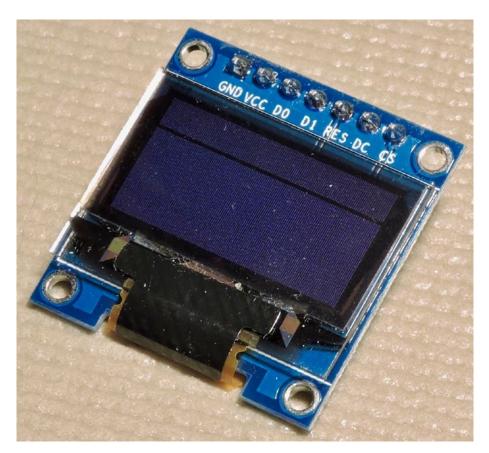

| OLED Display                                                                                                                                                                                     | 223                                                                                     |

| Configuration                                                                                                                                                                                    |                                                                                         |

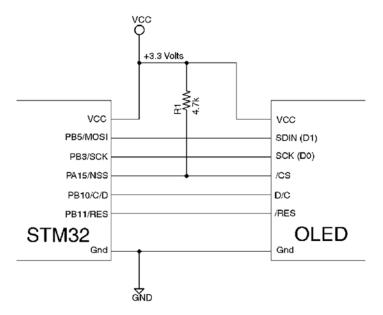

| Display Connections                                                                                                                                                                              |                                                                                         |

| Display Features                                                                                                                                                                                 |                                                                                         |

| Demo Schematic                                                                                                                                                                                   |                                                                                         |

| AFIO                                                                                                                                                                                             |                                                                                         |

| Graphics                                                                                                                                                                                         |                                                                                         |

| The Pixmap                                                                                                                                                                                       |                                                                                         |

| Pixmap Writing                                                                                                                                                                                   |                                                                                         |

| The Meter Software                                                                                                                                                                               |                                                                                         |

| Main Module                                                                                                                                                                                      |                                                                                         |

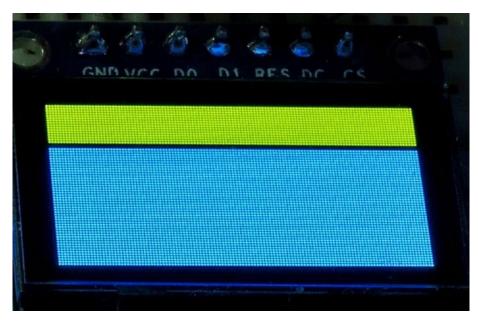

| Demonstration                                                                                                                                                                                    |                                                                                         |

| Summary                                                                                                                                                                                          |                                                                                         |

|                                                                                                                                                                                                  |                                                                                         |

| Chapter 13: OLED Using DMA                                                                                                                                                                       |                                                                                         |

| Chapter 13: OLED Using DMA<br>Challenges                                                                                                                                                         |                                                                                         |

|                                                                                                                                                                                                  | 241                                                                                     |

| Challenges                                                                                                                                                                                       |                                                                                         |

| Challenges<br>Circuit                                                                                                                                                                            |                                                                                         |

| Challenges<br>Circuit<br>DMA Operation                                                                                                                                                           |                                                                                         |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution                                                                                                                                          | 241<br>242<br>242<br>242<br>242<br>242<br>242<br>247                                    |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution<br>The Demonstration                                                                                                                     | 241<br>242<br>242<br>242<br>242<br>242<br>247<br>249                                    |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution<br>The Demonstration<br>Initializing DMA                                                                                                 | 241<br>242<br>242<br>242<br>242<br>242<br>247<br>249<br>250                             |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution<br>The Demonstration<br>Initializing DMA<br>Launching DMA                                                                                | 241<br>242<br>242<br>242<br>242<br>247<br>247<br>249<br>250<br>251                      |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution<br>The Demonstration<br>Initializing DMA<br>Launching DMA<br>OLED SPI/DMA Management Task                                                | 241<br>242<br>242<br>242<br>242<br>247<br>247<br>247<br>249<br>250<br>251<br>254        |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution<br>The Demonstration<br>Initializing DMA<br>Launching DMA<br>OLED SPI/DMA Management Task<br>DMA ISR Routine                             | 241<br>242<br>242<br>242<br>242<br>247<br>247<br>249<br>250<br>251<br>251<br>254        |

| Challenges<br>Circuit<br>DMA Operation<br>DMA Execution<br>The Demonstration<br>Initializing DMA<br>Launching DMA<br>OLED SPI/DMA Management Task<br>DMA ISR Routine<br>Restarting DMA Transfers | 241<br>242<br>242<br>242<br>242<br>247<br>249<br>250<br>251<br>251<br>254<br>255<br>256 |

| Chapter 14: Analog-to-Digital Conversion |  |

|------------------------------------------|--|

| STM32F103C8T6 Resources                  |  |

| Demonstration                            |  |

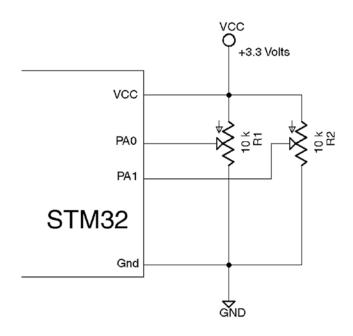

| Analog Inputs PA0 and PA1                |  |

| ADC Peripheral Configuration             |  |

| Demonstration Run                        |  |

| Reading ADC                              |  |

| Analog Voltages                          |  |

| Summary                                  |  |

| Bibliography                             |  |

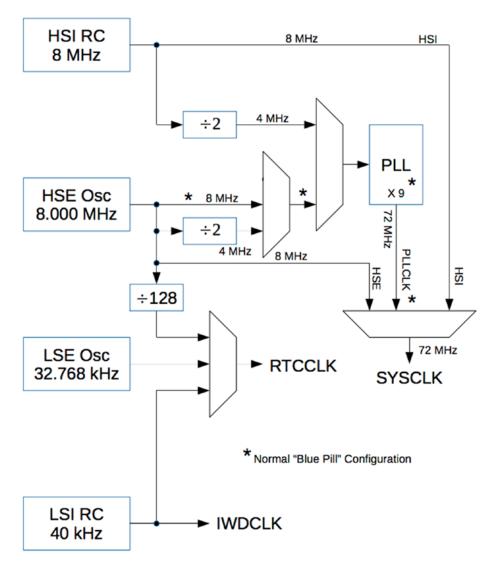

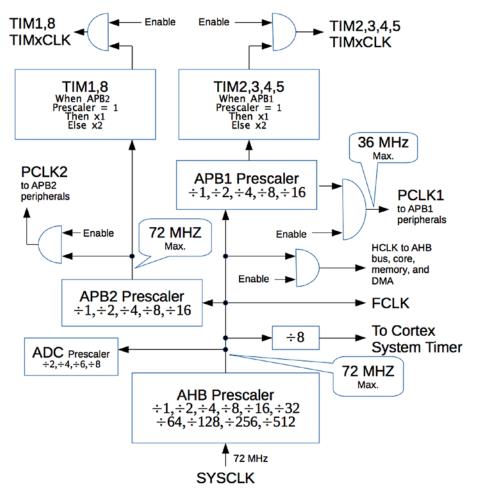

| Chapter 15: Clock Tree                   |  |

| In the Beginning                         |  |

| RC Oscillators                           |  |

| Crystal Oscillators                      |  |

| Oscillator Power                         |  |

| Real-time Clock                          |  |

| Watchdog Clock                           |  |

| System Clock (SYSCLK)                    |  |

| SYSCLK and USB                           |  |

| AHB Bus                                  |  |

| rcc_clock_setup_in_hse_8mhz_out_72mhz()  |  |

| APB1 Peripherals                         |  |

| APB2 Peripherals                         |  |

| Timers                                   |  |

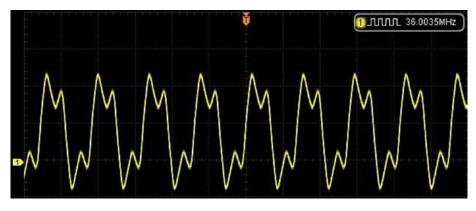

| rcc_set_mco()                            |  |

| HSI Demo                                 |  |

| HSE Demo                                 |  |

| PLL ÷ 2 Demo                             |  |

| Summary                                  |  |

| Bibliography                             |  |

| Chapter 16: PWM with Timer 2       |  |

|------------------------------------|--|

| PWM Signals                        |  |

| Timer 2                            |  |

| PWM Loop                           |  |

| Calculating Timer Prescale         |  |

| 30 Hz Cycle                        |  |

| Servo Hookup                       |  |

| Running the Demo                   |  |

| PWM on PB3                         |  |

| Other Timers                       |  |

| More PWM Channels                  |  |

| Summary                            |  |

| Bibliography                       |  |

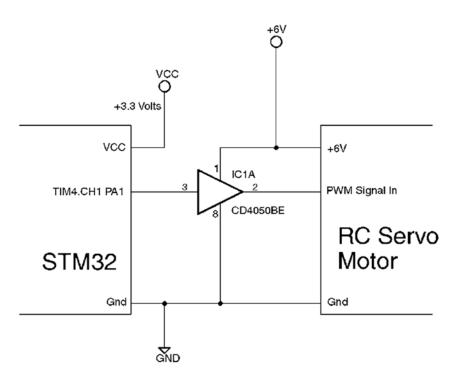

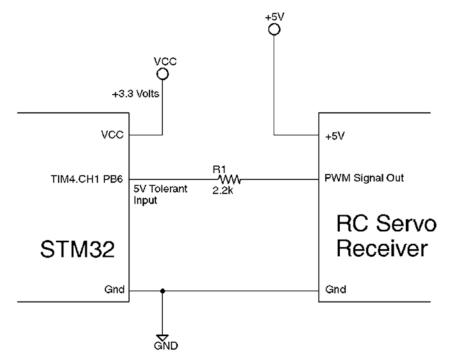

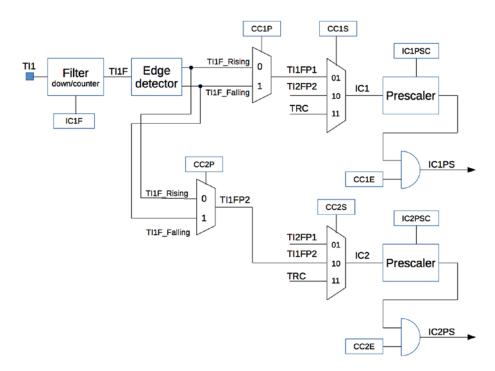

| Chapter 17: PWM Input with Timer 4 |  |

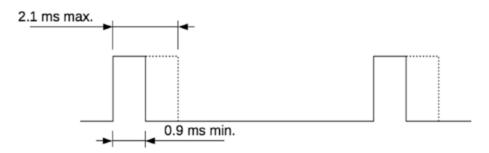

| The Servo Signal                   |  |

| Signal Voltage                     |  |

| Demo Project                       |  |

| GPIO Configuration                 |  |

| Timer 4 Configuration              |  |

| Task1 Loop                         |  |

| ISR Routine                        |  |

| Demonstration Run                  |  |

| Session Output                     |  |

| Timer Inputs                       |  |

| Summary                            |  |

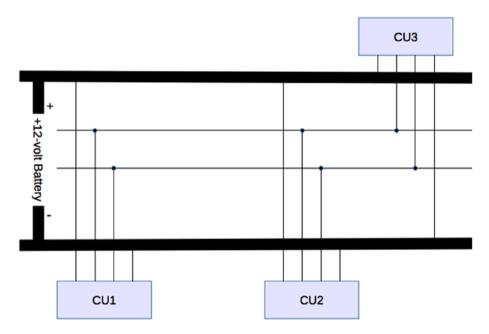

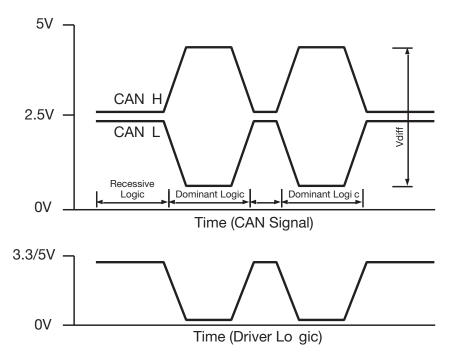

| Chapter 18: CAN Bus                |  |

| The CAN Bus                        |  |

| Differential Signals               |  |

| Dominant/Recessive                 |  |

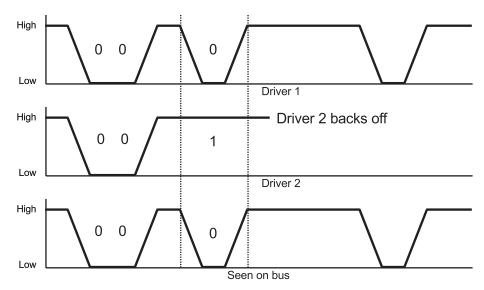

| Bus Arbitration              | 321        |

|------------------------------|------------|

| Synchronization              |            |

| Message Format               | 323        |

| STM32 Limitation             |            |

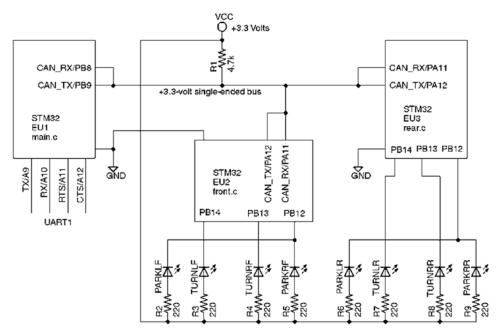

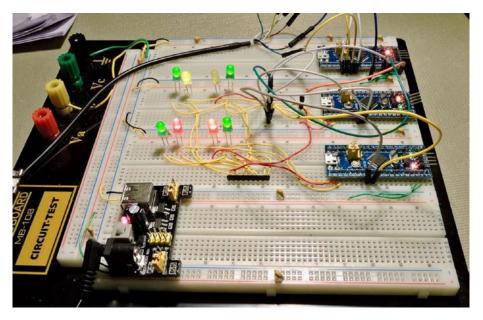

| Demonstration                | 325        |

| Software Build               | 325        |

| UART Interface               |            |

| MCU Flashing                 |            |

| Demo Bus                     |            |

| Session Run                  | 328        |

| CAN Messages                 | 330        |

| Synchronicity                |            |

| Summary                      | 331        |

| Bibliography                 | 331        |

| Chapter 19: CAN Bus Software | 333        |

|                              |            |

| can_init()                   |            |

| CAN Receive Filters          |            |

| CAN Receive Interrupts       |            |

| Application Receiving        |            |

| Sending CAN Messages         |            |

| Summary                      |            |

|                              |            |

| Chapter 20: New Projects     |            |

| Project Creation             |            |

|                              | 010        |

| Makefile                     |            |

| Included Makefiles           |            |

|                              |            |

| Included Makefiles           | 351<br>351 |

| FreeRTOS                     | 353 |

|------------------------------|-----|

| rtos/opencm3.c               | 353 |

| rtos/heap_4.c                | 354 |

| Required Modules             | 354 |

| FreeRTOSConfig.h             | 355 |

| User Libraries               | 357 |

| Rookie Mistakes              | 358 |

| Summary                      | 358 |

| Bibliography                 | 358 |

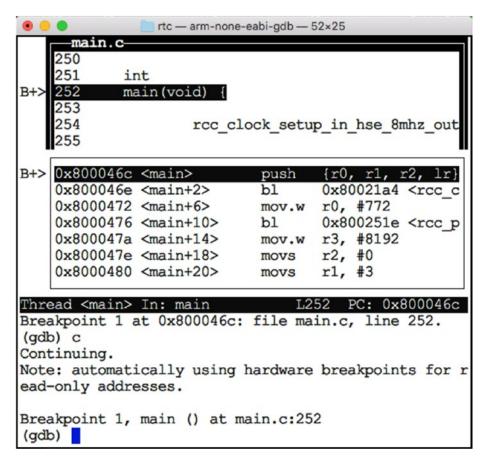

| Chapter 21: Troubleshooting  |     |

| Gnu GDB                      |     |

| GDB Server                   |     |

| Remote GDB                   | 363 |

| GDB Text User Interface      |     |

| Peripheral GPIO Trouble      | 367 |

| Alternate Function Fail      |     |

| Peripheral Fail              | 369 |

| ISR FreeRTOS Crash           | 369 |

| Stack Overflow               | 370 |

| Estimating Stack Size        |     |

| When a Debugger Doesn't Help |     |

| Push/Pull or Open Drain      |     |

| Peripheral Defects           |     |

| Resources                    |     |

| libopencm3                   | 373 |

| FreeRTOS Task Priorities     |     |

| Scheduling Within libopencm3 | 376 |

| Summary                      |     |

| Appendix A: Answers to Exercises    |  |

|-------------------------------------|--|

| Chapter 4                           |  |

| Chapter 5                           |  |

| Chapter 6                           |  |

| Chapter 7                           |  |

| Chapter 8                           |  |

| Chapter 9                           |  |

| Chapter 10                          |  |

| Chapter 11                          |  |

| Chapter 12                          |  |

| Chapter 13                          |  |

| Chapter 14                          |  |

| Chapter 15                          |  |

| Chapter 16                          |  |

| Chapter 17                          |  |

| Chapter 19                          |  |

| Chapter 20                          |  |

| Appendix B: STM32F103C8T6 GPI0 Pins |  |

| Index                               |  |

### **About the Author**

**Warren Gay** started out in electronics at an early age, dragging discarded TVs and radios home from public school. In high school he developed a fascination for programming the IBM 1130 computer, which resulted in a career-plan change to software development. Since graduating from Ryerson Polytechnical Institute, he has enjoyed a 30-plus-year software developer career, programming mainly in C/C++. Warren has been programming Linux since 1994 as an open source contributor and professionally on various Unix platforms since 1987.

Before attending Ryerson, Warren built an Intel 8008 system from scratch before there were CP/M systems and before computers got personal. In later years, Warren earned an advanced amateur radio license (call sign VE3WWG) and worked the amateur radio satellites. A high point of his ham-radio hobby was making digital contact with the Mir space station (U2MIR) in 1991.

Warren works at Datablocks.net, an enterprise-class ad-serving software services company where he programs C++ server solutions on Linux back-end systems.

### **About the Technical Reviewer**

**Stewart Watkiss** is a keen maker with a particular interest in physical computing. He earned a master's degree in electronic engineering from the University of Hull in 1996 and a master's degree in computer science from the Georgia Institute of Technology in 2017.

Most of his projects are based around the Raspberry Pi, which he creates alone or together with his two children. He has also created projects based around the Arduino and other platforms. Many of his projects are available on his website, www.penguintutor.com, which also provides tutorials on Linux and electronics. He is the author of the book *Learn Electronics with Raspberry Pi*, published by Apress.

Stewart also volunteers as a STEM Ambassador, working with local schools and educational events to enthuse children about programming and physical computing.

#### **CHAPTER 1**

## Introduction

There is considerable interest in the ARM Cortex platform today because ARM devices are found everywhere. Units containing ARM devices range from the small microcontroller embedded systems to cellphones and larger servers running Linux. Soon, ARM will also be present in higher numbers in the datacenter. These are all good reasons to become familiar with ARM technology.

With the technology ranging from microcontrollers to full servers, the question naturally arises: "Why study embedded device programming? Why not focus on end-user systems running Linux, like the Raspberry Pi?"

The simple answer is that embedded systems perform well in scenarios that are awkward for larger systems. They are frequently used to interface with the physical world. They go between the physical world and a desktop system, for example. The humble keyboard uses a dedicated MCU (microcontroller unit) to scan key switches of the keyboard and report key-press events to the desktop system. This not only reduces the amount of wiring necessary but also frees the main CPU from expending its highperformance computing on the simple task of noticing key-press events.

Other applications include embedded systems throughout a factory floor to monitor temperature, security, and fire detection. It makes little sense to use a complete desktop system for this type of purpose. Stand-alone embedded systems save money and boot instantly. Finally, the MCU's small size makes it the only choice in flying drones where weight is a critical factor.

The development of embedded systems traditionally required the resources of two disciplines:

- Hardware engineer

- Software developer

Frequently, one person is assigned the task of designing the end product. Hardware engineers specialize in the design of the electronic circuits involved, but eventually the

product requires software. This can be a challenge because software people generally lack the electronics know-how while the engineers often lack the software expertise. Because of reduced budgets and delivery times, the electronics engineer often becomes the software engineer as well.

There is no disadvantage to one person's performing both design aspects as long as the necessary skills are present. Whether you're an electronics engineer, software developer, hobbyist, or maker, there is nothing like real, down-to-earth practice to get you going. That is what this book is all about.

#### STM32F103C8T6

The device chosen for this book is the STMicroelectronics STM32F103C8T6. This part number is a mouthful, so let's break it down:

- STM32 (STMicroelectronics platform)

- F1 (device family)

- 03 (subdivision of the device family)

- C8T6 (physical manifestation affecting amount of SRAM, flash memory, and so on)

As the platform name implies, these devices are based upon a 32-bit path and are considerably more powerful than 8-bit devices as a result.

The F103 is one branch (F1 + 03) of the STM32 platform. This subdivision decides the CPU and peripheral capabilities of the device.

Finally, the C8T6 suffix further defines the capabilities of the device, like the memory capacity and clock speeds.

The STM32F103C8T6 device was chosen for this book because of the following factors:

- *very* low cost (as low as \$2 US on eBay)

- availability (eBay, Amazon, AliExpress, etc.)

- advanced capability

- form factor

The STM32F103C8T6 is likely to remain the lowest-cost way for students and hobbyists alike to explore the ARM Cortex-M3 platform for quite some time. The device is readily available and is extremely capable. Finally, the form factor of the small PCB allows header strips to be soldered to the edges and plugged into a breadboard. Breadboards are the most convenient way to perform a wide array of experiments.

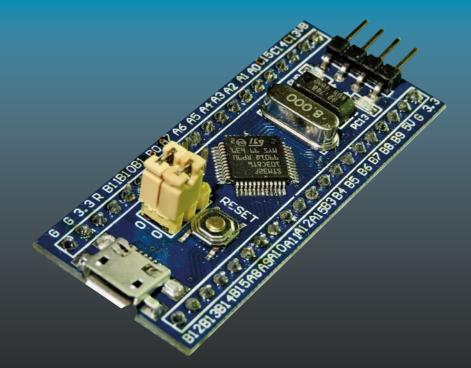

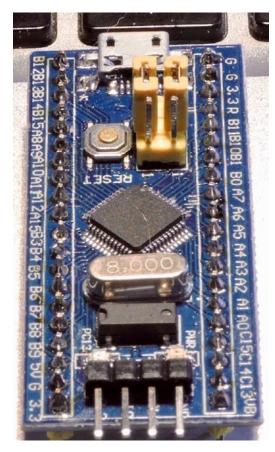

The MCU on a blue PCB (Figure 1-1) is affectionately known as the "Blue Pill," inspired by the movie *The Matrix*. There are some older PCBs that were red in color and were referred to as the "Red Pill." There are still others, which are black and are known as the "Black Pill." In this book, I'll be assuming you have the Blue Pill model. Apart from some USB deficiencies, there should be little other difference between it and the other models.

*Figure 1-1.* The STM32F103C8T6 PCB (printed circuit board) with the header strips soldered in, often referred to as the "blue pill"

Low cost has another advantage—it allows you to own *several* devices for projects involving CAN communications, for example. This book explores CAN communication using three devices connected by a common bus. Low cost means not being left out on a student budget.

The peripheral support of the STM32F103 is simply amazing when you consider its price. Peripherals included consist of:

- 4 x 16-bit GPIO Ports (most are 5-volt tolerant)

- 3 x USART (Universal Synchronous/Asynchronous Receiver/ Transmitter)

- 2 x I2C controllers

- 2 x SPI controllers

- 2 x ADC (Analog Digital Converter)

- 2 x DMA (Direct Memory Address controllers)

- 4 x timers

- watch dog timers

- 1 x USB controller

- 1 x CAN controller

- 1 x CRC generator

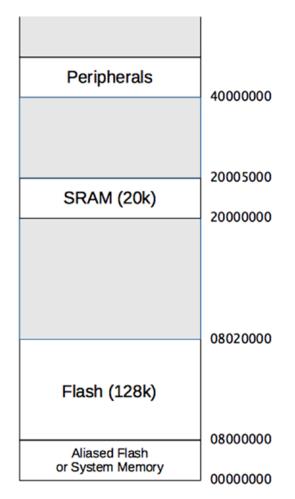

- 20K static RAM

- 64K (or 128K) FLASH memory

- ARM Cortex M3 CPU, max 72 MHz clock

There are some restrictions, however. For example, the USB and CAN controllers cannot operate at the same time. Other peripherals may conflict over the I/O pins used. Most pin conflicts are managed through the AFIO (Alternate Function Input Output) configuration, allowing different pins to be used for a peripheral's function.

In the peripheral configuration, several separate clocks can be individually enabled to tailor power usage. The advanced capability of this MCU makes it suitable for study. What you learn about the STM32F103 family can be leveraged later in more advanced offerings like the STM32F407.

The flash memory is officially listed at 64K bytes, but you may find that it supports 128K. This is covered in Chapter 2 and permits good-sized applications to be flashed to the device.

### **FreeRTOS**

Unlike the popular AVR family of chips (now owned by Microchip), the STM32F103 family has enough SRAM (static RAM) to comfortably run FreeRTOS (freertos.org). Having access to a RTOS (real-time operating system) provides several advantages, including

- preemptive multitasking;

- queues;

- mutexes and semaphores; and

- software timers.

Of particular advantage is the multitasking capability. This eases the burden of software design considerably. Many advanced Arduino projects are burdened by the use of state machines with an *event loop model*. Each time through the loop, the software must poll whether an event has occurred and determine if it is time for some action. This requires management of state variables, which quickly becomes complex and leads to programming errors. Conversely, preemptive multitasking provides separate control tasks that clearly implement their independent functions. This is a proven form of software abstraction.

FreeRTOS provides preemptive multitasking, which automatically shares the CPU time among configured tasks. Independent tasks, however, do add some responsibility for safely interacting between them. This is why FreeRTOS also provides message queues, semaphores, mutexes, and more to manage that safely. We'll explore RTOS capabilities throughout this book.

### libopencm3

Developing code for MCU applications can be demanding. One portion of this challenge is developing with the "bare metal" of the platform. This includes all of the specialized peripheral registers and their addresses. Additionally, many peripherals require a certain "dance" to make them ready for use.

This is where libopencm3 fits in (from libopencm3.org). Not only does it define the memory addresses for the peripheral register addresses, but it also defines macros for special constants that are needed. Finally, the library includes tested C functions for interacting with the hardware peripheral resources. Using libopencm3 spares us from having to do all of this from scratch.

### **No Arduino**

There is no Arduino code presented in this book. Arduino serves its purpose well, allowing students to wade into the MCU world without prior knowledge. This book, however, is targeted to go beyond the Arduino environment using a professional mode of development independent of Arduino tools.

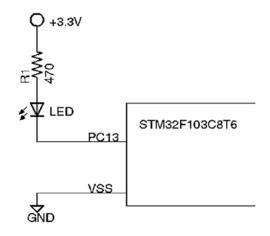

Without Arduino, there is no "digital port 10." Instead, you work directly with an MCU port and optionally a pin. For example, the Blue Pill device used in this book has the built-in LED on port C, as pin 13. Operating directly with ports permits I/O operations with all 16 pins at one time when the application needs it.

### No IDE

There was a conscious decision to choose for this book a development environment that was neutral to your desktop development platform of choice. There are a number of Windows-based IDE environments available, with varying licenses. But IDEs change, licenses change, and their associated libraries change with time. The advantage of the given IDE is often discarded when the IDE and the operating system it runs upon change.

Using a purely open sourced approach has the advantage that you are shielded from all this version churn and burn. You can mothball all of your code and your support tools, knowing that they can all be restored to operation ten years from now, if required. Restoring licensed software, on the other hand, leaves you vulnerable to expired licenses or online sites that have gone dark.

This book develops projects based upon the following open sourced tools and libraries:

- gcc/g++ (GNU compiler collection: open sourced)

- make (GNU binutils: open sourced)

- libopencm3 (library: open sourced)

- FreeRTOS (library: open source and free for commercial use)

With this foundation, the projects in this book should remain usable long after you purchase this book. Further, it permits Linux, FreeBSD, and MacOS users—in addition to those using the Windows platform—to use this book. If you do use Windows, you may

want to download and install the Cygwin environment (www.cygwin.com) because a Linux-like environment is assumed for the demo project builds.

All of the projects presented make use of the GNU (GNU is not Unix) make utility, which provides several build functions with minimum effort. If the provided builds in this book present errors, then make sure to use the GNU make command, especially on FreeBSD. Some systems install GNU make as gmake.

### **Development Framework**

While it is possible to make gcc, libopencm3, and FreeRTOS work together on your own, it does require a fair amount of organization and effort. How much is your time worth?

Rather than do this tedious work, a development framework is available for free from github.com for download. This framework integrates libopencm3 with FreeRTOS for you. Also provided are the make files needed to build the whole project tree at once or each project individually. Finally, there are some open source library routines included that can shorten the development time of your new applications. This framework is included as a github.com download or with the book's own source code download.

### **Assumptions About You**

This book is targeted to an audience wanting to go beyond the Arduino experience. This applies to hobbyists, makers, and engineers alike. The software developed in this book uses the C programming language, so fluency there will be helpful. Likewise, some basic digital electronics knowledge is assumed as it pertains to the peripheral interfaces provided by the platform. Additional light theory may be found in areas like the CAN bus, for example.

The STM32 platform can be a challenge to configure and to get operating correctly. Much of this challenge is the result of the extreme *configurability* of the peripheral devices. Each portion depends upon a clock, which must be enabled and divisor configured. Some devices are further affected by upstream clock configurations. Finally, each peripheral itself must be enabled and configured for use. You won't have to be an expert, because these ducks-in-a-row procedures will be laid out and explained in the chapters ahead.

Hobbyists and makers need not find the book difficult. Even when challenged, they should be able to build and *run* each of the project experiments. As knowledge and confidence builds, each reader can grow into the topics covered. As part of this exploration, all readers are encouraged to modify the projects presented and run further experiments. The framework provided will also allow you to create new ready-to-go projects with a minimum of effort.

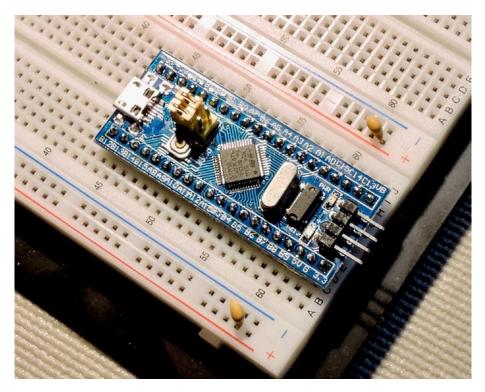

### What You Need

Let's briefly cover some items that you might want to acquire. Certainly, number one on the list is the Blue Pill device (see Figure 1-1). I recommend that you purchase units that include the header strips to be soldered onto the PCB so that you can easily use the unit on a breadboard (or presoldered, if you prefer).

These units are Buy-it-Now priced on eBay at around \$2.13 US, with free shipping from various sellers. To find these deals, simply use the part number STM32F103C8T6 for your search. Chapters 18–19 use three of these units communicating with each other over a CAN bus. If you'd like to perform those experiments, be sure to obtain at least three units. Otherwise, the demo projects only involve one unit at a time. A spare is always recommended in case of an unhappy accident.

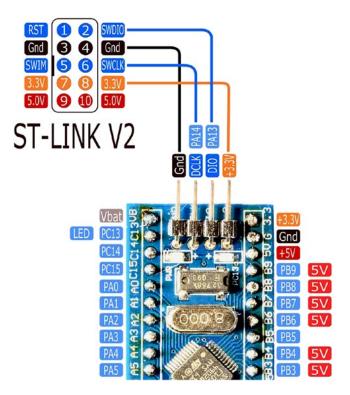

#### **ST-Link V2 Programming Unit**

The next essential piece of hardware is a programming adapter. Fortunately, these are also very economically priced. These can be found on eBay for about \$2.17 US, with free shipping. Simply search for "ST-Link." Be sure to get the "V2" programmer since there is no point in using the inferior older unit.

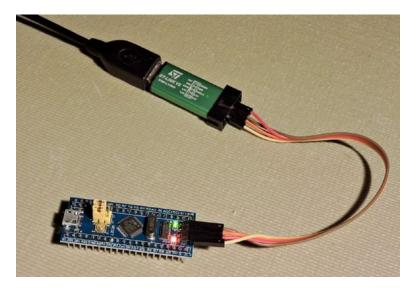

Most auctions will include four detachable wires to connect the unit to your STM32 device. Try to buy a unit that includes these unless you already have a cable. Figure 1-2 illustrates the USB programmer, usable from Windows, Raspberry Pi, Linux, MacOS, and FreeBSD.

Figure 1-2. ST-Link V2 programmer and cable

The STM32F103C8T6 device can be programmed in multiple ways, but this book will only use the ST-Link V2 USB programmer. This will simplify things for you when doing project development and allows remote debugging.

A USB extension cable is useful with this unit. If you don't have one, you might consider getting one.

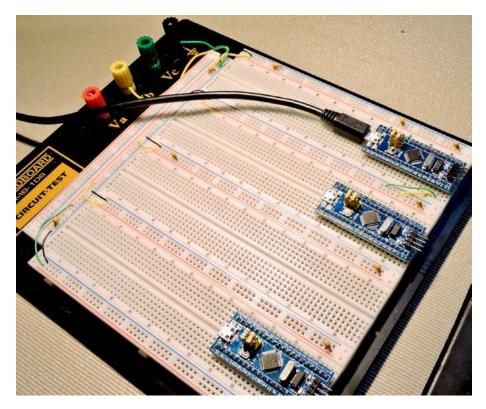

#### **Breadboard**

This almost goes without saying, but a breadboard is necessary to prototype experiments. The breadboard is a solderless way to quickly wire up experiments, try them, and then pull out the wires for the next experiment.

Many of the projects in this book are small, requiring space for one Blue Pill device and perhaps some LEDs or a chip or two. However, other experiments, like the one in Chapters 18–19, use three units communicating with each other over a CAN bus.

I recommend that you obtain a breadboard that will fit four units (this leaves a little extra hookup space). Alternatively, you could simply buy four small breadboards, though this is less convenient.

Figure 1-3 illustrates the breadboard that I am using in this book. It is not only large enough, but also has power rails at the top and bottom of each strip. The power rails are recommended, since this eases the wiring.

Figure 1-3. A breadboard with supply rails

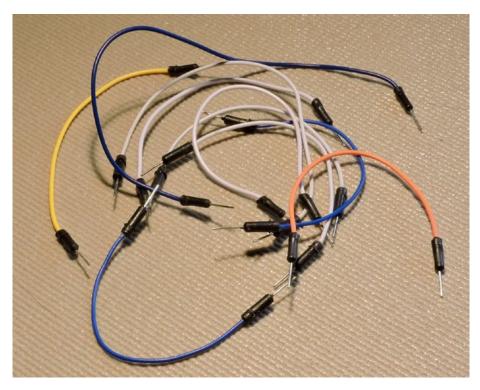

#### **DuPont (Jumper) Wires**

You might not give much thought to the wiring of a breadboard, but you will find that DuPont wires can make a huge difference. Yes, you can cut and strip your own AWG22 (or AWG24) gauge wires, but this is inconvenient and time consuming. It is far more convenient to have a small box of wires ready to go. Figure 1-4 illustrates a small random collection of DuPont wires.

Figure 1-4. A random collection of DuPont wires

Male-to-male DuPont wires can be purchased in assorted sets on eBay for about the Buy-it-Now price of \$2.00 US with free shipping. They might have auction titles like "65Pcs Male to Male Solderless Flexible Breadboard DuPont Jumper Cable Wires." I recommend that you get the *assorted* sets so that you get different colors and lengths. A search like "DuPont wires male -female" should yield good results. The "-female" keyword will eliminate any ads that feature female connectors.

### 0.1 uF Bypass Capacitors

You might find that you can get by without bypass caps (capacitors), but they are recommended (shown in Figure 1-5 as yellow blobs on the power rails). These can be purchased in quantity from various sources, including eBay.

*Figure 1-5.* Breadboard with STM32F103C8T6 and 0.1 uF bypass capacitors installed on the rails

Try to buy quality capacitors like Metalized Polyester Film units if possible. The voltage rating can be as low as 16 volts. A few of these should be plugged into your supply rails on the breadboard, between the positive and negative rails, to filter out any voltage transients and noise.

### **USB TTL Serial Adapter**

This device is essential for some of the projects in this book. Figure 1-6 illustrates the unit that I used. This serial adapter is used to communicate data to your desktop/laptop. Without a display, this allows you to communicate through a virtual serial link (via USB) to a terminal program.

There are several types of these available on eBay and elsewhere, but be careful to get a unit with *hardware flow control signals*. The cheapest units will lack these additional signals (look for RTS and CTS). Without hardware flow control signals, you will not be able to communicate at high speeds, such as 115200 baud, without losing data.

If you're running Windows, also be careful of buying FTDI (FTDI Chip) fakes. There were reports of FTDI software drivers bricking the fake devices at one time. Your choice doesn't have to include FTDI, but if the device claims FTDI compatibility, be aware and check your driver support.

You'll notice in Figure 1-6 that I have a tag tied to the end of the cable. That tag reminds me which colored wire is which so that I can hook it up correctly. You might want to do something similar.

Figure 1-6. A USB-to-TTL serial (5V) adapter cable

These are normally 5-volt devices and are hence TTL compatible. Note, however, that one of the features of the STM32F103 family of devices is that many of the GPIO pins are 5-volt tolerant, even though the MCU operates from a +3.3-volt supply. This permits the use of these TTL adapters without causing harm. More will be said about this later. Other units can be purchased that operate at the 3.3-volt level or that can switch between 5 and 3.3 volts.

### **Power Supply**

Most of the projects presented will run just fine off of the USB or TTL adapter power output. But if your project draws more than the usual amount of current, then you may need a power adapter. Figure 1-7 illustrates a good adapter to fit the breadboard power rails. It can be purchased from eBay for about \$1.00 US with free shipping. Mine was advertised as "MB102 Solderless Breadboard Power Supply Module, 3.3V 5V for Arduino PCB Board." If your breadboard lacks power rails, you may need to shop for a different type of breadboard.

Figure 1-7. A small breadboard power supply and 7.5 VDC adapter

The MB102 is convenient because it can be jumpered to supply 3.3 or 5 volts. Additionally, it includes a power on/off button.

The other consideration is the *wall adapter* to supply the *input* power (this is not included). While the MB102 accepts up to 12 volts of input, I found that most 9 VDC wall adapters had an open circuit voltage near 13 volts or more. I feel that those are risky because if the cheap MB102 fails for any reason, the over-voltage might leak through and damage your MCU unit(s) as well.

Foraging through my junk box of "wall warts," I eventually found an old Ericsson phone charger rated at 7.5 VDC at 600 mA. It measured an unloaded voltage of 7.940 volts. This is much closer to the 5 and 3.3 volt outputs that the MB102 will regulate to. If you have to purchase a power adapter, I recommend a similar unit.

### Small Stuff

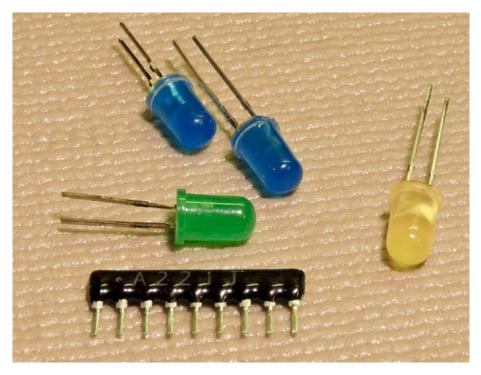

There are some small items that you may already have. Otherwise, you will need to get some LEDs and resistors for project use. Figure 1-8 shows a random set of LEDs and a SIP-9 resistor.

Figure 1-8. A random collection of 5 mm LEDs and one SIP-9 resistor at the bottom

Usually an LED is targeted for about 10 mA of current for normal brightness. Smaller LEDs only require maybe 2 to 5 mA. With a supply voltage near 3.3 volts, you'll want a resistor of about 220  $\Omega$  to limit the current (220 ohms limits the current to a maximum of approximately 7 mA). So, get a few 220  $\Omega$  resistors (1/8th watt will be sufficient).

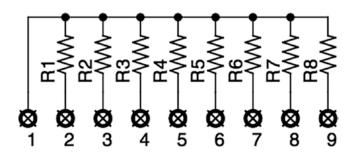

Another part you may want to consider stocking is the SIP-9 resistor. Figure 1-9 illustrates the internal schematic for this part. If, for example, you want to drive eight LEDs, you would need eight current-limiting resistors. Individual resistors work but require extra wiring and take up breadboard space. The SIP-9 resistor, on the other hand, has one connection common to the eight resistors. The other eight connections are the other end of the internal resistors. Using this type of package, you can reduce the parts count and wiring required.

Figure 1-9. The internal schematic view of a SIP-9 resistor

### Summary

This chapter has introduced the main actors that will appear in this book. It also itemized most of the things that you might need to acquire. The next chapter will guide you through the necessary steps of software installation. Once that is out of the way, the real fun can begin.

#### **CHAPTER 2**

# **Software Setup**

Before you can get underway with project-related work, you need some software installed. There are a number of "moving parts" involved. Despite this, the process should proceed smoothly. Once accomplished, it need not be revisited.

### **Directory Conventions Used**

Throughout this book, I'll need to refer to different subdirectories of the supplied software. It is assumed that the top level of your installed software is named "~/stm32f103c8t6." So, when I refer to a pathname "~/stm32f103c8t6/libopencm3/README.md," I'll assume that starts from your home (~) directory (wherever that is). I'll often use this pathname convention for clarity, even though your current directory may be the correct one for the file being referenced.

### **Operating Software**

I'm also going to assume you have a POSIX (Linux/Unix) environment from which to run commands. The Linux or Raspberry Pi environments using the bash shell are perhaps the most natural. Other good environments include FreeBSD and MacOS. From FreeBSD, I'll assume that you are using the bash shell.

If you're using Windows and you haven't installed it yet, you'll want to install Cygwin (https://www.cygwin.com). Some might use MSYS instead. After installing the base Cygwin system, make sure that you also install make and git. This will give you a Linux-like command-line environment from which to build software.

#### CHAPTER 2 SOFTWARE SETUP

Mac users will need to install git at a minimum. You'll also need GNU make, especially if you use FreeBSD (Free Berkeley Software Distribution). Sometimes GNU make is installed as gmake instead on a BSD (Berkely Software Distribution) system. If you're using Mac Homebrew (https://brew.sh), you can install these as follows:

```

$ brew install make

$ brew install git

```

If you're a Mac Ports (https://www.macports.org) user, you'll need to use that framework to install make and git.

# **Book Software**

The directory structure for building with libopencm3 and FreeRTOS is available from github.com. Choose a suitable place from which to create a subdirectory. This book will assume home directory:

\$ cd ~

Use the git command to download and create a subdirectory as follows:

```

$ git clone https://github.com/ve3wwg/stm32f103c8t6.git

```

The preceding command will create directory ~/stm32f103c8t6. However, feel free to rename it to something easier to type, like ~/stm32.

#### libopencm3

Next, we must download the libopencm3 software into the correct place. First, change to the subdirectory, and then issue the git clone command for libopencm3:

```

$ cd ~/stm32f103f8t6

```

```

$ git clone https://github.com/libopencm3/libopencm3.git

```

This will populate the directory ~/stm32f103c8t6/libopencm3 with files and subdirectories.

#### **FreeRTOS**

The next important piece of software is FreeRTOS. Unfortunately, it must be downloaded and unpacked as a zip file.

- 1. Go to http://www.freertos.org.

- 2. Locate "Download Source" at the left.

- 3. Click the link "2. Click to download the latest official release from SourceForge."

Depending on your browser and operating system, a zip file should be downloaded automatically. It will have a version number in the file name. At the time of writing, the downloaded file name is FreeRTOSv10.0.1.zip. Change to the ~/stm32f103c8t6/rtos subdirectory before unpacking the zip file. On my Mac, the download directory is ~/Downloads. Substitute in the unzip command as required for your system:

```

$ cd ~/stm32f103c8t6/rtos

$ unzip ~/Downloads/FreeRTOSv10.0.1.zip

```

Once that completes, there should be several files and subdirectories under ~/stm32f103c8t62/rtos/FreeRTOSv10.0.1.

#### ~/stm32f103c8t6/rtos/Project.mk

Because the version number of FreeRTOS is included in the subdirectory name, there is a potential change left. Edit the file Project.mk with your favorite editor (or nano) and locate the following line near the top of the file:

FREERTOS ?= FreeRTOSv10.0.1

If your version of FreeRTOS is newer than this, like FreeRTOSv11.0.0, then edit it to match your version and resave the file:

FREERTOS ?= FreeRTOSv11.0.0

This will allow the Project.mk make file to work correctly later when you want to create a new RTOS project.

# **ARM Cross Compiler**

If you don't yet have an ARM cross compiler installed, it will need to be installed. If you're running Linux or Raspberry Pi, you may be able to just use the apt-get command to install it. Despite that, I recommend that you download and install the toolchain as outlined next instead because some cross-compiler tools are not well organized and are sometimes incomplete.

If you're running Mac or Windows (Cygwin), then definitely use the following procedure. This procedure is also recommended for Linux and Raspberry Pi if you have had problems with the installed packages:

- 1. Go to the site https://developer.arm.com.

- 2. Click on the link "Linux/Open Source."

- 3. Scroll down and click on "ARM GNU Embedded Toolchain."

- 4. Scroll down and click on the big button labeled "Downloads."

- 5. Scroll down until you find the platform download required. Windows 32-bit, Linux 64-bit, Mac OS X 64-bit, etc. Click on the appropriate choice for your platform to download.

- 6. Create a system directory /opt (if you do not already have one):

```

$ sudo -i

# mkdir /opt

```

7. Change to the /opt directory (as root):

# cd /opt

8. From this point, you'll unpack your compiler download (Mac example). Be sure to be specific about your home directory:

```

# tar xjf ~myuserid/Downloads/gcc-arm-none-eabi-6-2017-q2-

update-mac.tar.bz2

```

Use tar option "j" if the ending of the file is .bz2. Otherwise, use "z" when the ending is .gz. If you don't have the GNU tar command installed on the Mac, then you can install it using macports (www.macports.org) or Homebrew (https://brew.sh/). 9. Once the tar file has been extracted, it may produce a large directory name like gcc-arm-none-eabi-6-2017-q2-update. Now is a good time to shorten that:

# mv gcc-arm-none-eabi-6-2017-q2-update gcc-arm

This will rename the directory /opt/gcc-arm-none-eabi-6-2017q2-update to a more manageable name /opt/gcc-arm.

10. Now, exit root and return to your developer session. In that session, add the compiler's bin directory to your PATH:

\$ export PATH="/opt/gcc-arm/bin:\$PATH"

11. At this point, you should be able to test your cross compiler:

\$ arm-none-eabi-gcc --version arm-none-eabi-gcc (GNU Tools for ARM Embedded Processors 6-2017-q2-update) 6.3.1 20170620 (release) [ARM/embedded-6-branch revision 249437] Copyright (C) 2016 Free Software Foundation, Inc. This is free software; see the source for copying conditions. There is NO warranty; not even for MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

If the compiler doesn't start and instead gives you a message like this:

```

$ arm-none-eabi-gcc --version

-bash: arm-none-eabi-gcc: command not found

```

then your PATH variable is either not set up properly or not exported, or the installed tools are using a different prefix. Perform the following if necessary (the output has been abbreviated slightly here):

```

$ ls -l /opt/gcc-arm/bin

total 75128

-rwxr-xr-x@ 1 root wheel 1016776 21 Jun 16:11 arm-none-eabi-addr2line

-rwxr-xr-x@ 2 root wheel 1055248 21 Jun 16:11 arm-none-eabi-ar

-rwxr-xr-x@ 2 root wheel 1749280 21 Jun 16:11 arm-none-eabi-as

```

```

-rwxr-xr-x@ 2 root

wheel

1206868 21 Jun 19:08 arm-none-eabi-c++

1016324 21 Jun 16:11 arm-none-eabi-c++filt

-rwxr-xr-x@ 1 root

wheel

wheel

1206788 21 Jun 19:08 arm-none-eabi-cpp

-rwxr-xr-x@ 1 root

-rwxr-xr-x@ 1 root

wheel

42648 21 Jun 16:11 arm-none-eabi-elfedit

wheel

1206868 21 Jun 19:08 arm-none-eabi-g++

-rwxr-xr-x@ 2 root

-rwxr-xr-x@ 2 root

wheel

1202596 21 Jun 19:08 arm-none-eabi-gcc

. . .

-rwxr-xr-x@ 2 root wheel 1035160 21 Jun 16:11 arm-none-eabi-nm

-rwxr-xr-x@ 2 root wheel 1241716 21 Jun 16:11 arm-none-eabi-objcopy

. . .

```

If you obtained your cross compiler from a different source than the one indicated, you might not have the prefix names. If you see the file name gcc instead of arm-none-eabi-gcc, you'll need to invoke it as simply gcc. *But be careful in this case*, because your cross compiler may get confused with your *platform* compiler. The prefix arm-none-eabi- prevents this. When you go to use your cross platform gcc, check that the correct compiler is being used with the type command:

```

$ type gcc

arm-none-eabi-gcc is hashed (/opt/gcc-arm/bin/gcc)

```

If your bash shell is locating gcc from a different directory than the one you installed, then your PATH is not set correctly.

If you must change the toolchain prefix, then the top-level ~/stm32f103c8t6/ Makefile.incl should be edited:

```

$ cd ~/stm32f103c8t6

$ nano Makefile.incl

```

Modify the following line to suit and resave it:

PREFIX ?= arm-none-eabi

In a normal situation where the cross-platform prefix is used, you should also be able to make this confirmation:

```

$ type arm-none-eabi-gcc

arm-none-eabi-gcc is hashed (/opt/gcc-arm/bin/arm-none-eabi-gcc)

```

This confirms that the compiler is being run from the installed /opt/gcc-arm directory.

**Note** The PATH variable will need modification for each new terminal session to use the cross-compiler toolchain. For convenience, you may want to create a script, modify your ~/.bashrc file, or create a shell alias command to do this.

#### **Build the Software**

At this point, you've installed the book software, libopencm3, FreeRTOS, and the ARM cross-compiler toolchain. With the PATH variable set (as just seen), you should now be able to change to your stm32f103c8t6 directory and type make (some users might need to use gmake instead):

```

$ cd ~/stm32f103c8t6

```

\$ make

This will build ~/stm32f103c8t6/libopencm3 first, followed by all other subdirectories.

There is always the possibility that a new version of libopencm3 might create build problems. These are difficult to anticipate, but here are some possibilities and solutions:

- 1. Something in libopencm3 is flagged as an error by the cross compiler, where previously it was acceptable. You can:

- a. Correct or work around the problem in the libopencm3 sources.

- b. Try a later (or prior) version of the cross-compiler toolchain. Newer toolchains will often correct the issue. For reference, the toolchain used for this book was "GNU Tools for ARM Embedded Processors 6-2017-q2-update) 6.3.1 20170620."

- c. Install an older version of libopencm3. All projects tested in this book used the library with the latest git commit dated October 12, 2017.

- Something in the book's software is busted. Check the git repository for updates. As issues become known, fixes will be applied and released there. Also check the top-level README.md file.

# **ST-Link Tool**

There is one final piece of software that may need installation. If you've not already installed it using your system's package manager, you'll need to install it now. Even if you have it installed already, it may be outdated. Let's test it to see:

```

$ st-flash

```

Look for the following line in the help display:

```

./st-flash [--debug] [--reset] [--serial <serial>] [--format <format>] \

[--flash=<fsize>] {read|write} <path> <addr> <size>

```

If you don't see the option --flash=<fsize> mentioned, then you may want to download the latest from github and build it from source code. This is only necessary if you want to use more than 64K of flash memory. None of the demos in this book go over that limit.

People have reported that many of the STM32F103C8T6 units support 128K of flash memory, even though the device reports that it only has 64K. The following command probes a unit that I own, from eBay, for example:

```

$ st-info --probe

Found 1 stlink programmers

serial: 493f6f06483f53564554133f

openocd: "\x49\x3f\x6f\x06\x48\x3f\x53\x56\x45\x54\x13\x3f"

flash: 65536 (pagesize: 1024)

sram: 20480

chipid: 0x0410

descr: F1 Medium-density device

```

The information reported indicates that the device only supports 65536 bytes (64K) of flash. Yet, I know that I can flash up to 128K and use it (all of mine support 128K). It has been suggested that both the F103C8 devices and the F103B8 devices use the same silicon die. I'll cover using the ST-Link V2 programmer on your device in the next chapter.

If you don't have these utilities installed, do so now using apt-get, brew, yum, or whatever your package manager is. Failing a package install, you can download the latest source code from github here:

```

$ cd ~

$ git clone https://github.com/texane/stlink.git

$ cd ./stlink

$ make

$ cd build/Release

```

```

$ sudo make install

```

If you run into trouble with this, see the following online resources:

- The README.md file at https://github.com/texane/stlink

- https://github.com/texane/stlink/blob/master/doc/compiling.md

- Make sure that you have libusb installed.

- Some Linux distributions may require you to also perform sudo 1dconfig after the install.

### Summary

With the software installs out of the way, we can finally approach the hardware and do something with it. In the next chapter, we'll look at your power options and then apply the ST-Link V2 programmer to probe your device.

## **CHAPTER 3**

# **Power Up and Blink**

The unit that you purchased has likely already been preprogrammed to blink when it is powered up (perhaps you've checked this already). This makes it easy to test that it is a working unit. There are a few other important details regarding power, reset, and LEDs that need to be discussed in this chapter. Finally, the use of the ST-Link V2 programmer and a device probe will be covered.

## Power

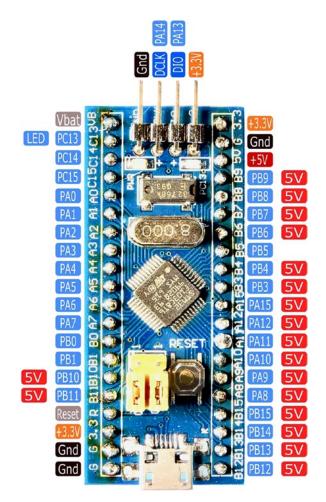

The STM32F103C8T6 PCB, otherwise known as the "Blue Pill" board, has a number of connections, including a few for power. It is not necessary to use all of the power connections at once. In fact, it is best to use only one set of connections. To clarify this point, let's begin with an examination of your power options. Figure 3-1 illustrates the connections around the edges of the PCB, including power.

**Figure 3-1.** Power and GPIO connections to the STM32F103C8T6 "Blue Pill" PCB. Power can be supplied to a +5V, +3.3V, or USB port, with the matching voltage. Pins marked as "5V" (with no plus sign) are 5-volt tolerant inputs. Pins marked with a plus sign are for power input.

The four pins at the top end of the board (darker blue) are used for programming the device. Notice that the programming connection labeled DIO is also capable of being a GPIO PA13. Likewise, DCLK is capable of being a GPIO PA14. You'll discover how configurable the STM32 can be as we go through this book.

At the programming connector, note that the input supply voltage is +3.3 volts. This connection is electrically the same as any of the others that are labeled "+3.3V" around the PCB. These are shown in a light orange.

#### +3.3V Regulator

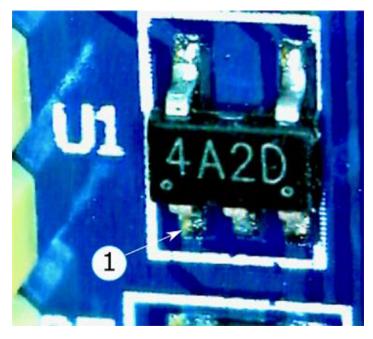

The STM32F103C8T6 chip is designed to operate from any voltage from 2 to 3.3 volts. The Blue Pill PCB provides a tiny +3.3-volt regulator labeled "U1" on the underside (see Figure 3-2). My unit used a regulator with an SMD code of 4A2D, which is an XC6204 series part. Yours may vary.

*Figure 3-2.* The +3.3-volt regulator on the underside of the PCB. Pin 1 of the 4A2D (XC6204 series) regulator chip is marked.

The official schematic for this board specifies the regulator as being the RT9193-33, which supports 300 mA.<sup>1</sup> It is possible that my PCB is a clone using a cheaper regulator chip. My XC6204 series regulator chip is limited to 150 mA. Unless you know the specifics of your unit, it is safest to assume 150 mA is the current limit.

The power performance of the MCU will be examined in a later chapter. But as a starting reference point, the blink program in the device as supplied uses about 30 mA (measured with the +5-volt input supply at 4.97 volts). This measurement includes the small additional current used by the regulator itself.

The datasheet for the STM32F103C8T6 documents the maximum current draw at about 50 mA. This document measurement was obtained with the external clock and

#### CHAPTER 3 POWER UP AND BLINK

all peripherals enabled, while operating in "run mode" at 72 MHz. Subtracting 50 from your regulator max of 150 leaves you a current budget of about 100 mA from the +3.3-volt regulator. It's always good to know what the limits are!

#### **USB Power/+5V**

When powered by a USB cable, the power arrives by the Micro-USB B connector. This +5-volt supply is regulated to the +3.3 volts needed by the MCU. Similarly, at the top right of Figure 3-1, there is a pin labelled "+5V" (with a plus sign), which can be used as a power input. This goes to the same regulator input that the USB connector supplies.

Because of the low current requirements of your MCU, you can also power the unit from a TTL serial adapter. Many USB serial adapters will have a +5-volt line available that can supply your MCU. Check your serial adapter for specifications to be certain.

Be careful *not* to connect a USB cable and supply +5 volts *simultaneously*. Doing so could cause damage to your desktop/laptop through the USB cable. For example, if your +5-volt supply is slightly higher in voltage, you will be injecting current into your desktop USB circuit.

#### +3.3V Supply

If you have a +3.3-volt power supply, you can leave the +5V inputs *unconnected*. Connect your +3.3-volt power supply directly to the +3.3V input (make sure that the USB cable is *unplugged*). This works because the regulator disables itself when there is no input provided on the 5-volt input.

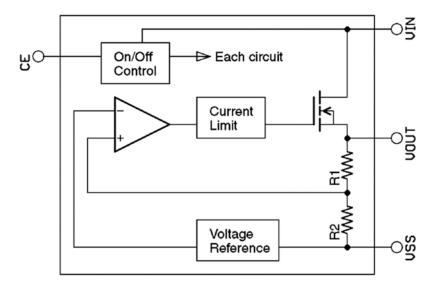

When supplying power to the +3.3-volt input, you are connecting your power to the VOUT terminal of the regulator shown in Figure 3-3. In this case, there is no 5-volt power flowing into VIN of the regulator. The CE pin is also connected to VIN, but when VIN is unconnected, the CE pin becomes grounded by a capacitor. A low level on CE causes the regulator to shut down its internal subsystems.

Figure 3-3. Block diagram of the 5 to 3.3 volt regulator

There is, however, a small amount of current flow into the regulator's voltage divider. This current will flow from your +3.3 volts to ground, through *internal* resistances R1 and R2 of the regulator. These resistances are high, and the current involved is negligible. But be aware of this when measuring current for ultra-low-power battery applications.

**Caution** Do not supply both +5 volts and +3.3 volts at the same time. This could cause damage to the regulator or your desktop when the USB cable is plugged in. Use a single power source.

#### **One Power Source Rule**

What I've been leading up to is the general advice to use just *one power source*. I can't stress enough that supplying your PCB with more than one power source can cause damage.

This tends to be obvious with the +3.3-volt and +5-volt supply inputs. What can *easily* be forgotten, however, is the *USB cable*. Consider that you could have power arriving from a USB serial adapter, the ST-Link V2 programmer, or the USB cable. Move slowly when changing your power arrangement, especially when switching from programming the device to your normal power configuration.

#### CHAPTER 3 POWER UP AND BLINK

Certain applications may require you to use additional supplies; for example, when powering motors or relays. In those cases, you would supply the *external* circuits with the power they need but not the MCU PCB. Only the signals and the ground need to share connections. If this isn't clear, then assume the one power source rule.

# Ground

The return side of the power circuit, or the negative side, is known as the ground connection. It is labeled in Figure 3-1 in black. All of these ground connections are electrically connected together. These pins can be used interchangeably.

# Reset

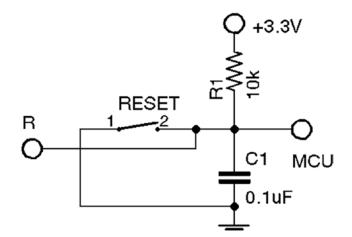

The PCB also supplies a button labeled "RESET" and a connection on one side labeled "R." This connection permits an external circuit to reset the MCU if required. Figure 3-4 illustrates the push-button circuit, including the connection going to the MCU.

*Figure 3-4. The STM32F103C8T6 Reset circuit. Connection "R" is found on the edge of the PCB.*

# Showtime

You've probably already tested your unit, but if you haven't yet then do so now. The safest and easiest way to do this is to use a USB cable with a Micro-USB B connector. Plug your cable into a USB power source, which doesn't have to be a computer.

Once powered, your unit should blink away. If not, then try pressing the Reset button. Also make sure that your boot-0 and boot-1 jumpers are positioned as shown in Figure 3-1 (both jumpers should be positioned to the side labeled "0").

There are two built-in LEDs. The LED on the left indicates that power has been applied (mine was yellow, but yours may differ). The LED at right is activated by GPIO port PC13 under program control (mine was red; again, yours may differ).